服务热线:0755 28160800

地址:中国 深圳市 宝安区石岩

街道水田社区第二工业区

业务直线电话:

(86)0755-28160800

(86)0755-29839665

(86)0755-29839692

业务传真:(86)755 2344-2951

前台电话:(86)0755-29839341

前台传真:(86)755-2983-9345

邮箱:ytsales@www.ecccar.com

而那边,台积电已经宣布了2nm工艺取得了重大突破,预计在2024年投入量产。

在失去华为这个重要客户之后,台积电并没有像预想那样受一定的影响,反倒依靠手里5nm工艺这张王牌,在市场上遥遥领先于竞争对手三星。

10nm、7nm、5nm、3nm、2nm……在摩尔定律进展放缓的同时,台积电突破半导体工艺进步的脚步却从未放慢。

本月苹果秋季发布会,没了万众期待的iPhone12系列,性能强大的A14处理器便成了主角。使用5nm制程工艺的A14到底有多强大——封装118亿个晶体管;性能比上一代提升40%;16核神经网络引擎,每秒可执行11万亿次操作。

但在强大性能的背后,受制于5nm工艺的高成本和较低的成品率,5nm芯片的产能十分有限。新闻媒体报道表示,今年台积电最多只能代工7400万颗A14处理器,这还是在动用全部5nm产能下能完成的数量。

在美国对华为制裁禁令的生效之后,台积电已无法再为华为代工麒麟芯片,此前华为给台积电的订单是1500万颗麒麟5nm芯片,但因为生产时间十分有限,最终也只在9月15日之前生产了880万颗处理器,占据全部订单的60%左右。在这之后,台积电也将全部产能投入到A14处理器的生产中。

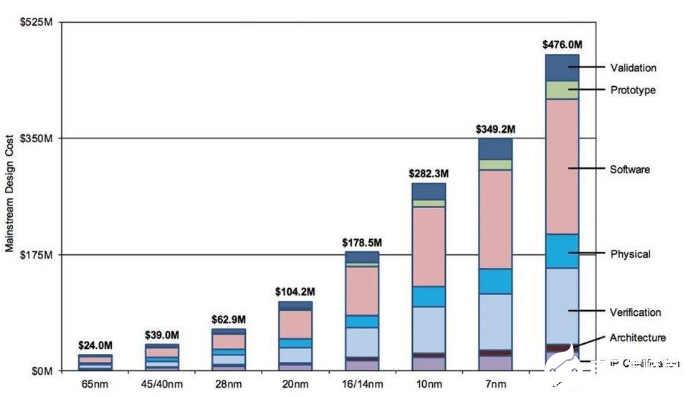

昂贵的设备和工艺成本,推动了芯片价格的上涨,这是没办法避免的。正如2018年的时候,台积电官方表示,预计在5nm工艺上总共投资了250亿美元,其中5nm芯片设计成本将增至4.76亿美元。也就是说,像设计一款A14或者麒麟5nm芯片,总成本可能高达近5亿美元。

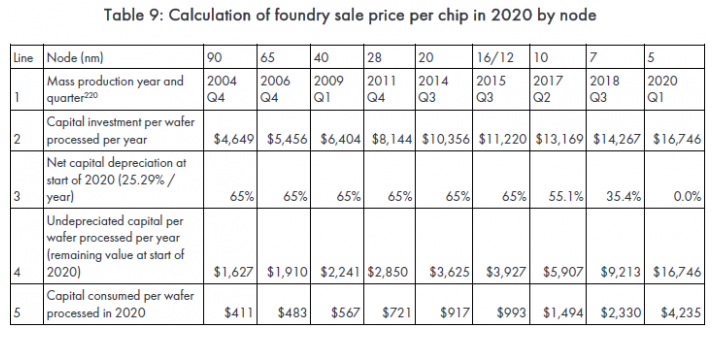

在美国研究机构CSET的两位作者编写的一份题为《AIChips: What They Are and Why They Matter》的报告中,他们借助模型预估得出,台积电5nm制造的12吋晶圆成本约为16988美元,远高于7nm约为9346美元的成本。

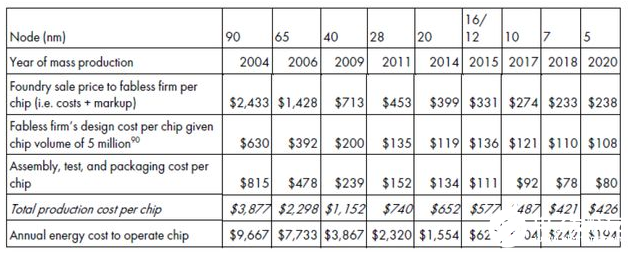

如果换算成单颗5nm芯片的制造成本,同样也十分昂贵。每片300mm直径的晶圆只可以制造71.4颗5nm芯片,平摊单颗芯片成本将高达238美元(约合1600块钱)。

报告以英伟达P100GPU为例,这款产品采用台积电的16nm节点处制造,包含了153亿个晶体管,裸片面积为610平方毫米。

事实上这还只是晶圆制造成本,而一颗芯片的诞生还需要包含设计成本和封装、测试成本,这部分的成本也是非常高的,每颗芯片的设计和封装、测试成本,分别为108美元和80美元。

如果这份研究报告的准确性高的线nm芯片支付的总成本将可能达到426美元(约为2929元)。

当然,这么估算也只是最理想的状态,考虑到5nm工艺才开始正式量产,所以可能会有比较高的损耗,同时光刻机的成本也极高,因为要重度依赖极紫外光EUV技术,而一台EUV光刻机的价格高达1.2亿美元。

实际上麒麟9000的成本可以并不是特别需要这么多。此前有人透露,12吋晶圆大概能够切割出400颗麒麟9000芯片。若按此计算,单颗制造成本为42美元,约合287块钱,加上设计和封装、测试成本,一颗芯片的最终成本可能在230美元左右,也就是1570元人民币。

市场研究机构International Business Strategies (IBS)给出的多个方面数据显示,28nm之后芯片的成本迅速上升。28nm工艺的成本为0.629亿美元,到了7nm和5nm,芯片的正本迅速暴增,5nm将增至4.76亿美元。三星称其3nm GAA 的成本可能会超过5亿美元。

并且,随着半导体复杂性的增加,对高品质人才的需求也一直增长,这也进一步推高了先进制程芯片的成本。报告中指出,研究人员的有效数,即用半导体研发支出除以高技能研究人员的工资,从1971年到2015年增长了18倍。

为了支撑先进制程,台积电十年内研发人数增加了三倍,2017年研发人员将近6200人,比2008年多了近两倍,这6200人只从事研发,不从事生产。

目前,台积电披露了旗下的又一大新研发进展,即3nm工艺。这一工艺台积电去年就开始着手,目前进展顺利。

与5nm相比,3nm可以在相同的功率水平下提高10-15%的性能,或者在相同的晶体管速度下降低25-30%的功率。其计划在2021年进入风险生产,2022年下半年进入量产。

台积电在2nm半导体制造节点方面取得重大研究突破,有望在2023年中期进入2nm工艺试生产阶段,并在一年后开始批量生产。目前,台积电的最新制造工艺是5nm工艺,已用来生产A14仿生芯片。

据悉,台积电的2nm工艺将采用差分晶体管设计,采用环绕闸极(GAA)制程为基础的MBCFET架构,解决FinFET因制程微缩产生电流控制漏电的物理极限问题。而在极紫外光微显影技术方面的进步让台积电的 纳米片(Nano Sheet)堆叠关键技术更为成熟,良品率的提升比预期的顺利许多。

该设计被称为多桥沟道场效应(MBCFET)晶体管,它是对先前FinFET设计的补充。有必要注意一下的是,这也是台积电第一次将MBCFET设计用于其晶体管。

台积电一位高管对外表示,“我们乐观预计2023年下半年风险试产收益率将达到90%,这将有利于我们未来继续赢得苹果、汇达等主要厂商的大订单”。同时,他还提到,量产将于2024年开始。

台积电去年成立了2nm项目研发团队,寻找可行的发展路径。考虑到成本、设备兼容性、技术成熟度和性能等条件,2nm采用了基于环绕门(GAA)工艺的MBCFET。

这方面最早的仍然是三星,三星已经准备在 3nm 工艺的时候引入 GAA 技术。基于全新的GAA晶体管结构,三星利用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),3nm 工艺可将核心面积减少 45%,功耗降低 50%,性能提升 35%。

至于台积电,一手消息显示,台积电有很大的可能性在 2nm 的时候在引入 GAA 技术。根据 Digitimes 报道,台积电 2nm GAA 工艺研发进度提前,目前已结束了路径探索阶段。

人员接手试产及量产作业的种子团队,推动新竹宝山和高雄厂于 2024年同步南北试产、2025年量产。 从1971的10000

先进制程决战2025 /

工艺不仅对晶圆厂来说是一个重大挑战,同样也考验着EDA公司,以及在此基础上设计芯片的客户。

,专家绞尽脑汁想尽各种办法,包括改变半导体材料、改变整体结构、引入新的工艺。但毋庸置疑的是,

的拐点 /

芯片何时出这样的一个问题目前没有相关官方的报道,因此无法给出准确的回答。根据网上的一些消息台积电于6月16日在2022年度北美技术论坛上首次宣布,将推出下一代先进工艺制程

可以容纳更多的晶体管在同样的芯片面积上,从而提供更高的集成度和解决能力。此外,较小的节点尺寸还能够更好的降低电路的功耗,提供更高的能效。可以说,

是如何消亡的? /

是近半个世纪以来,指导半导体行业发展的基石。它不仅是技术进步的预言,更是科技领域中持续创新的见证。要完全理解

的影响和意义,首先一定要了解它的起源、内容及其对整个信息技术产业的深远影响。

? /

并确保MOSFET晶体管最终成为有希望的候选材料,因为2D-FET提供固有的亚1

晶体管沟道厚度。它们适用于高性能和低功耗平台,因为它们拥有非常良好的载流子运输和移动性,即使是原子薄层也是如此。此外,它们的器件主体厚度和适中的能

? /

大战 全面打响 /

制程也将在2025年推出。但随着半导体线宽微缩越来越逼进物理极限,台积电还能继续维持高速成长,甩开对手吗?